#### Lecture – 3

Chapter 2: Sections 1 and 2

### Outline

- Boolean Algebra

- Basic Theorems and Properties of Boolean Algebra

- Boolean Functions

#### Digital circuit

- **Digital circuit:** hardware components that manipulate binary information.

- Each basic circuit: logic gate

- Each gate: performs a specific logical operation.

- Boolean Algebras:

- describe the operational properties of digital circuits

- specify the operation of each gate

- design logic circuit through the manipulation of Boolean expressions

#### **Binary Variables**

- Recall that the two binary values have different names:

- True/False

- o On/Off

- Yes/No

- 0 1/0

- We use 1 and 0 to denote the two values.

- Variable identifier examples:

- $\circ$  A, B, y, z, or X<sub>1</sub> for now

- RESET, START\_IT, or ADD1 later

#### **Logical Operations**

- The three basic logical operations are:

- o AND

- $\circ$  OR

- o NOT

- o NAND

- o NOR

- o XOR

- AND is denoted by a dot (·).

- OR is denoted by a plus (+).

- NOT is denoted by a single quote mark (') or an overbar ( -).

- NAND (.)'

- NOR (+)'

- XOR (+)

#### **Notation Examples**

• Examples:

```

Y = A . B is read "Y is equal to A AND B."

Z = x + y is read "z is equal to x OR y."

X = A' is read "X is equal to NOT A."

```

## **Gates**

Let's examine the processing of the following six types of gates

- 1. NOT

- 2. AND

- 3. OR

- 4. XOR

- 5. NAND

- 6. NOR

Typically, logic diagrams are black and white, and the gates are distinguished only by their shape

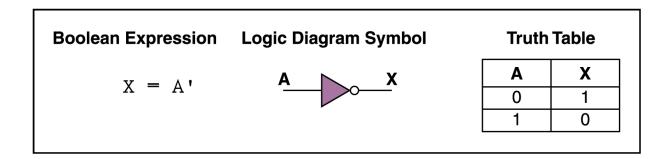

# **NOT Gate**

A NOT gate accepts one input value and produces one output value

By definition, if the input value for a NOT gate is 0, the output value is 1, and if the input value is 1, the output is 0

A NOT gate is sometimes referred to as an *inverter* because it inverts the input value

## **AND Gate**

An AND gate accepts two input signals.

If the two input values for an AND gate are both 1, the output is 1; otherwise, the output is 0

| Boolean Expression | Logic Diagram Symbol | т | ruth Tab | le |

|--------------------|----------------------|---|----------|----|

|                    | <b>А</b> X           | Α | В        | Х  |

| $X = Y \cdot B$    |                      | 0 | 0        | 0  |

|                    | В                    | 0 | 1        | 0  |

|                    |                      | 1 | 0        | 0  |

|                    |                      | 1 | 1        | 1  |

# **OR Gate**

If the two input values are **both** 0, the output value is 0; otherwise, the output is 1

| <b>Boolean Expression</b> | Logic Diagram Symbol | 7 | ruth Tab | le |

|---------------------------|----------------------|---|----------|----|

|                           | Av                   | Α | В        | X  |

| X = Y + B                 | ^                    | 0 | 0        | 0  |

|                           | В                    | 0 | 1        | 1  |

|                           |                      | 1 | 0        | 1  |

|                           |                      | 1 | 1        | 1  |

# **XOR Gate**

XOR, or exclusive OR, gate

- An XOR gate produces 0 if its **two inputs are the same**, and a 1 otherwise

- <u>Note</u> the difference between the XOR gate and the OR gate; they differ only in one input situation

- When both input signals are 1, the OR gate produces a 1 and the XOR produces a 0

| Boolean Expression | Logic Diagram Symbol | Т | ruth Tab | le |

|--------------------|----------------------|---|----------|----|

|                    | A X                  | Α | В        | Х  |

| $X = A \oplus B$   |                      | 0 | 0        | 0  |

|                    | В                    | 0 | 1        | 1  |

|                    |                      | 1 | 0        | 1  |

|                    |                      | 1 | 1        | 0  |

|                    |                      |   | ·        |    |

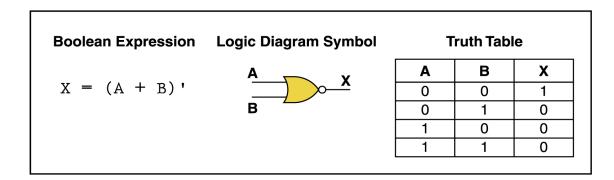

## **NAND and NOR Gates**

The NAND and NOR gates are essentially the **opposite** of the AND and OR gates, respectively

### **NAND Gate**

| Boolean Expression | Logic Diagram Symbol | т | ruth Tabl | le |

|--------------------|----------------------|---|-----------|----|

|                    | A x                  | Α | В         | Х  |

| $X = (A \cdot B)'$ |                      | 0 | 0         | 1  |

|                    | В                    | 0 | 1         | 1  |

|                    |                      | 1 | 0         | 1  |

|                    |                      | 1 | 1         | 0  |

|                    |                      |   |           |    |

## **NOR Gate**

# **Review of Gate Processing**

- A **NOT** gate **inverts** its single input value

- An AND gate produces 1 if both input values are 1

- An **OR** gate produces 1 if one or the other or both input values are 1

- An XOR gate produces 1 if one or the other (but not both) input values are 1

- A <u>NAND</u> gate produces the <u>opposite</u> results of an <u>AND</u> gate

- A **NOR** gate produces the **opposite** results of an **OR** gate

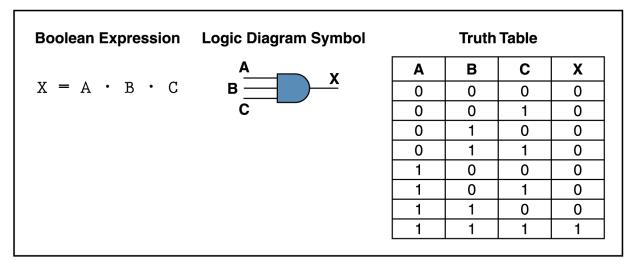

# **Gates with More Inputs**

- Gates can be designed to accept three or more input values

- A three-input AND gate, for example, produces an output of 1 only if all input values are 1

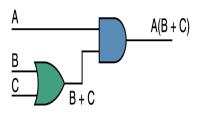

# **Combinational Circuits**

Gates are combined into circuits by using the output of one gate as the input for another

Consider the following Boolean expression A(B + C)

### The Truth table and the draw is:

| Α | В | С | B+C | A(B+C) |

|---|---|---|-----|--------|

| 0 | 0 | 0 | 0   | 0      |

| 0 | 0 | 1 | 1   | 0      |

| 0 | 1 | 0 | 1   | 0      |

| 0 | 1 | 1 | 1   | 0      |

| 1 | 0 | 0 | 0   | 0      |

| 1 | 0 | 1 | 1   | 1      |

| 1 | 1 | 0 | 1   | 1      |

| 1 | 1 | 1 | 1   | 1      |

## Boolean algebra

Boolean algebra allows us to apply provable mathematical principles to help us design logical circuits

An algebraic structure defined on a set of at least two elements  $B=\{0, 1\}$ , together with three binary operators (denoted +, · and ') that satisfies the following basic identities:

# **Properties of Boolean Algebra**

Closure: The structure is closed with respect to the operator +, ·, '

| Property       | AND                    | OR                        |

|----------------|------------------------|---------------------------|

| Commutative    | AB = BA                | A + B = B + A             |

| Associative    | (AB)C = A(BC)          | (A + B) + C = A + (B + C) |

| Distributive   | A(B + C) = (AB) + (AC) | A + (BC) = (A + B)(A + C) |

| Identity       | A1 = A                 | A + 0 = A                 |

| Complement     | A(A') = 0              | A + (A') = 1              |

| DeMorgan's law | (AB)' = A' OR B'       | (A + B)' = A'B'           |

### Theorem

1. (a)

$$X + X = X$$

(b)

$$X \cdot X = X$$

2. (a)

$$X + 1 = 1$$

(b)

$$X \cdot 0 = 0$$

3. (a)

$$(X')' = X$$

4.

$$(a)(X + Y) + Z = X + (Y + Z)(b)(XY)Z = X(YZ)$$

**Associative**

5.

$$(a)(X + Y)=X' Y'$$

(b)

$$(X \cdot Y) = X' + Y$$

6.

$$(a)\dot{X} + XY = X$$

(b)

$$\dot{X}(X+Y)=X$$

### **Boolean Operator Precedence**

The order of evaluation in a Boolean expression is:

- Parentheses

- NOT

- AND

- OR

**Consequence**: Parentheses appear around OR expressions

**Example:** F = A(B + C)(C + D')

**Example 1: Boolean Algebraic Proof**

$$x + x \cdot y = x$$

(Theorem 6(a))Proof StepsJustification $x = x + x \cdot y$ Our assertion (after commutation) $= x \cdot 1 + x \cdot y$ Identity Postulate $= x \cdot (1+y)$ Distributive Postulate $= x \cdot 1$ from definition of OR operation $= x$ Identity Postulate

## **Example 2: Boolean Algebra Proof**

x(x+y)=x (Theorem 6(b)): Let's use some truth tables to do this ... but first Proof Steps Justification x = x(x + y) Our assertion (after commutation)  $= x \cdot x + x \cdot y$  Distributive Postulate xx + xyXX X У XY. 0 0 0 0 0 0 1 0 0 0 1 0 1 0 1 1 1 1 1 1

### **Some Properties of Identities & the Algebra**

- If the **meaning is unambiguous**, we <u>leave out</u> the symbol "."

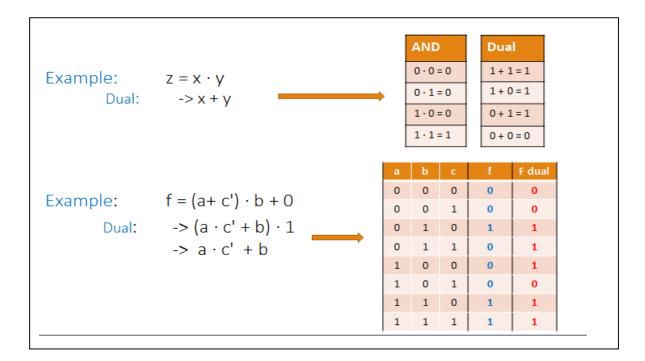

- **Duality principle**: The dual of a boolean algebraic expression is obtained by interchanging + and and interchanging 0's and 1's.

# **One more Dual**

Example:  $g = x \cdot y + (w + z)'$

Dual:  $\rightarrow (x + y) \cdot (w \cdot z)'$

| X | У | w | Z | g | g dual |

|---|---|---|---|---|--------|

| 0 | 0 | 0 | 0 | 1 | 0      |

| 0 | 0 | 0 | 1 | 0 | O      |

| 0 | 0 | 1 | 0 | 0 | 0      |

| 0 | 0 | 1 | 1 | 0 | 0      |

| 0 | 1 | 0 | 0 | 1 | 1      |

| 0 | 1 | 0 | 1 | 0 | 1      |

| 0 | 1 | 1 | 0 | 0 | 1      |

| 0 | 1 | 1 | 1 | О | O      |

| 1 | 0 | 0 | 0 | 1 | 1      |

| 1 | 0 | 0 | 1 | 0 | 1      |

| 1 | 0 | 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 1 | 0 | 0      |

| 1 | 1 | 0 | 0 | 1 | 1      |

| 1 | 1 | 0 | 1 | 1 | 1      |

| 1 | 1 | 1 | 0 | 1 | 1      |

| 1 | 1 | 1 | 1 | 1 | 0      |

### De Morgan's Laws (Theorem)

Formalization credited to Augustus De Morgan, a British mathematician.

He is also credited with initial work on the rules of mathematical induction.

In plain English we might say, "Since it is false that two things are both true, at least one of them must be false."

## The Laws:

The Not X or Y rule:

- NOR ( X, Y ) = AND( X', Y')

- $(X + Y)' = X' \cdot Y'$

The Not X and Y rule:

- NAND( X, Y ) = OR( X', Y')

- $(X \cdot Y)^{\dot{}} = X' + Y'$

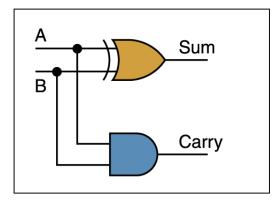

## **Adders**

- At the digital logic level, addition is performed in binary

- Addition operations are carried out by special circuits called, appropriately, <u>adders</u>

- The result of adding two binary digits could produce a <u>carry value</u>

- Recall that 1 + 1 = 10 in base two

| A | В | Sum | Carry |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 0   | 1     |

A circuit that computes the sum of two bits and produces the correct carry bit is called a <u>half adder</u>

Circuit diagram representing a half adder

Two Boolean expressions:

$$sum = A \oplus B$$

$carry = AB$

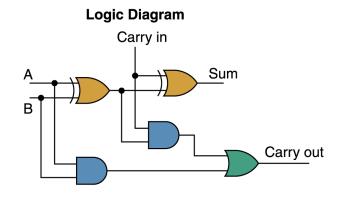

A circuit called a **full adder** takes the carry-in value into account

**Truth Table**

| Α | В | Carry-<br>in | Sum | Carry-<br>out |

|---|---|--------------|-----|---------------|

| 0 | 0 | 0            | 0   | 0             |

| 0 | 0 | 1            | 1   | 0             |

| 0 | 1 | 0            | 1   | 0             |

| 0 | 1 | 1            | 0   | 1             |

| 1 | 0 | 0            | 1   | 0             |

| 1 | 0 | 1            | 0   | 1             |

| 1 | 1 | 0            | 0   | 1             |

| 1 | 1 | 1            | 1   | 1             |

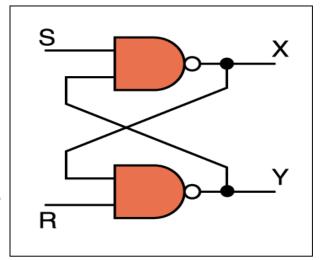

## **Circuits as Memory**

- Digital circuits can be used to store information

- These circuits form a sequential circuit, because the output of the circuit is also used as input to the circuit

- An S-R latch (Set-Reset) stores a single binary digit (1 or 0)

- There are several ways an S-R latch circuit could be designed using various kinds of gates

- The design of this circuit guarantees that the two outputs X and Y are always complements of each other

- The value of X at any point in time is considered to be the current state of the circuit

Therefore, if X is 1, the circuit is storing a 1; if X is 0, the circuit is storing a 0

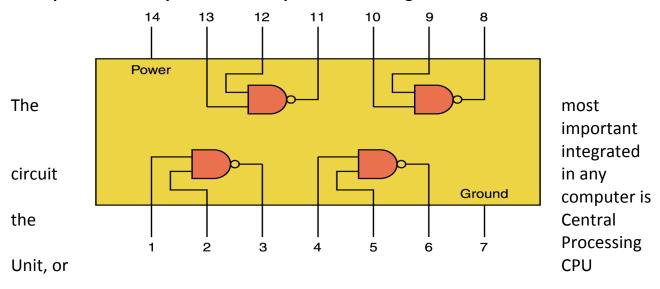

## **Integrated Circuits**

- Integrated circuit (also called a chip) A piece of silicon on which multiple gates have been embedded

- These silicon pieces are mounted on a plastic or ceramic package with pins along the edges that can be soldered onto circuit boards or inserted into appropriate sockets

- Integrated circuits (IC) are classified by the number of gates contained in them

| Abbreviation | Name                         | Number of Gates   |

|--------------|------------------------------|-------------------|

| SSI          | Small-Scale Integration      | 1 to 10           |

| MSI          | Medium-Scale Integration     | 10 to 100         |

| LSI          | Large-Scale Integration      | 100 to 100,000    |

| VLSI         | Very-Large-Scale Integration | more than 100,000 |

#### **Example: An SSI chip contains independent NAND gates**

Each CPU chip has a large number of pins through which essentially all communication in a computer system occurs