#### Lecture – 11 - Chapter 5

#### **Outline**

- sequential circuits

- storage elements: latch and flip-flop

- Sequential circuit analysis

- Moore and Mealy Models

- State tables

- State diagrams

#### **Introduction to Sequential Circuits**

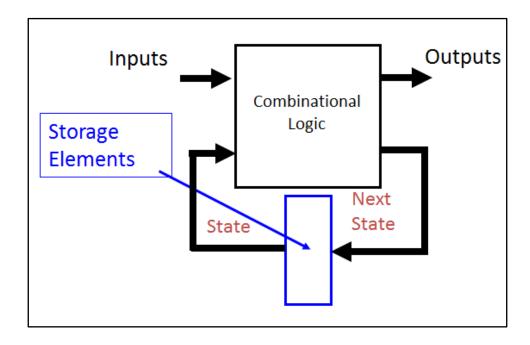

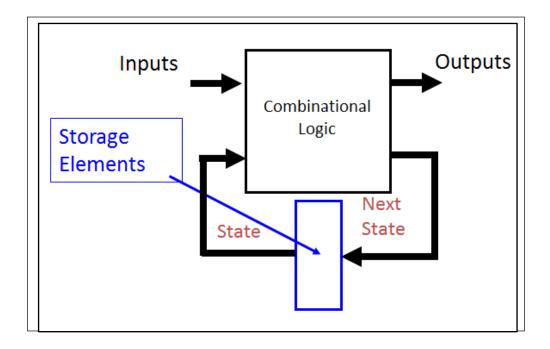

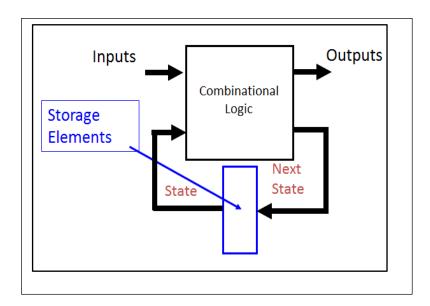

- A Sequential circuit contains:

- Storage elements:

Latches or Flip-Flops

- Combinational Logic:

- Implements a multiple-output switching function

- Signals from the outside are **inputs**.

- Signals to the outside are **outputs**.

- Other inputs, State or Present State, are signals from storage elements.

- The remaining outputs, Next State are inputs to storage elements.

# • Combinatorial Logic

- Next state functionNext State = f(Inputs, State)

- Output is a function of inputs and State.

#### Storage element

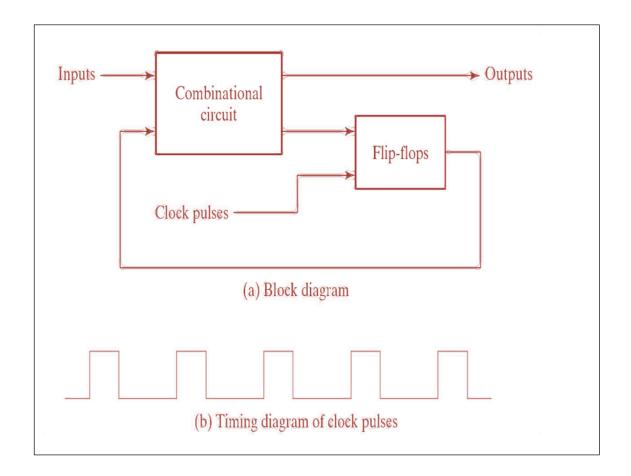

• **Storage elements:** devices capable of storing binary information

flip-flop: used in clocked sequential circuit, storing one bit of information: state

The flip-flop is updated when a pulse of the clock signal occurs.

Latch: basic component of flip-flop.

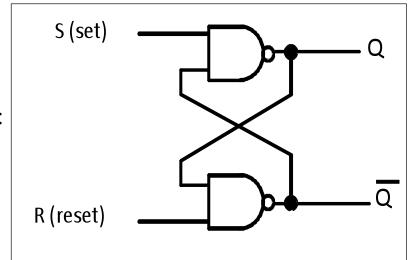

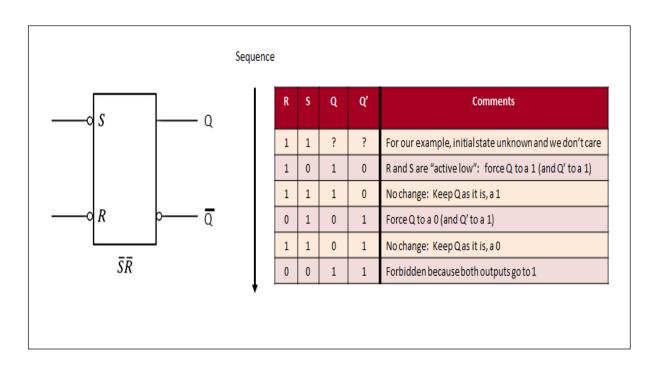

#### Basic (NAND) S – R (<u>Set-Reset latch</u>)Latch

• "Cross-Coupling" two NAND

gates gives the S'-R' (Set-Reset) Latch:

Which has the time sequence behavior:

S = 0, R = 0 is <u>forbidden</u> as input pattern

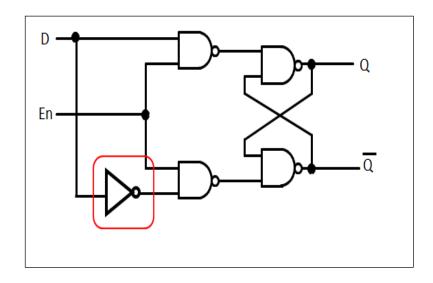

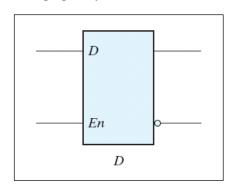

#### D Latch

• Adding an inverter to the S-R Latch, gives the D Latch

(shown with an enable input)

The graphic symbol for a D Latch is:

The enable input often acts as the clock.

• Note that there are no "indeterminate" states!

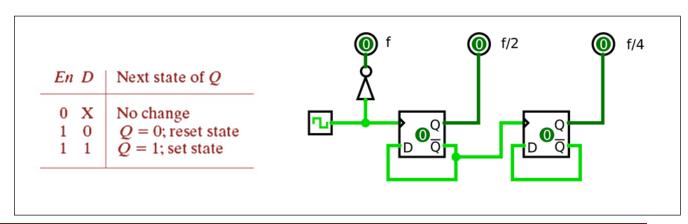

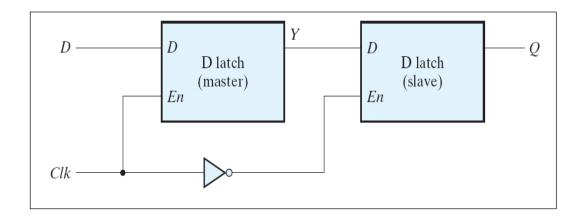

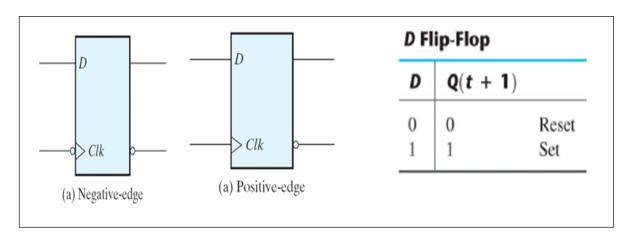

#### Edge-Triggered D Flip-Flop

• The edge-triggered D flip-flop is the master-slave D flip-flop

• The change of the D flip-flop output is associated with the negative (positive) edge at the end of the pulse

#### Sequential Circuit Analysis

- General Model

- Current State at time (t) is stored in flip-flops.

- Next State at time (t+1) is a Boolean function of State and Inputs.

- Outputs at time (t) are a Boolean function of State

(t) and (sometimes) Inputs (t).

#### Moore and Mealy Models

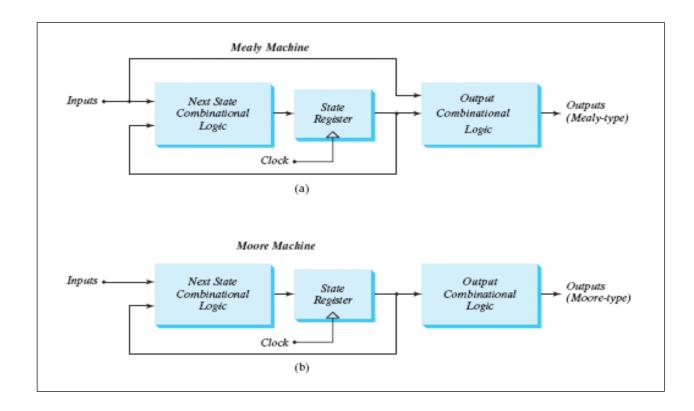

• Sequential Circuits or Sequential Machines are also called *Finite State Machines* (FSMs). Two formal models exist:

#### **Mealy Model**

- Named after G. Mealy

- Outputs are a function of <u>inputs</u> AND <u>states</u>

#### **Moore Model**

- Named after E.F. Moore

- Outputs are a function ONLY of states

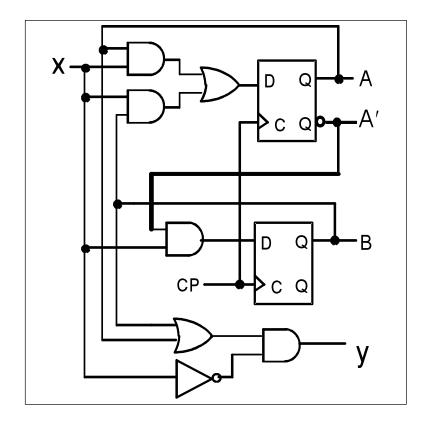

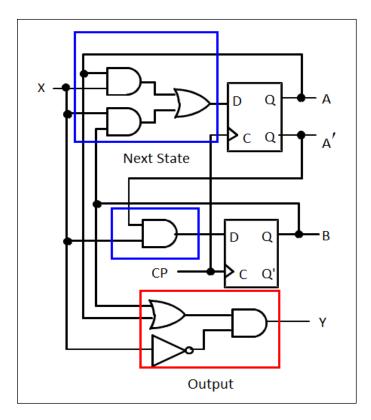

# Example 1

- <u>Input</u>: x

- Output: y

- <u>State:</u> (A, B)

- What is the <u>Output</u> <u>Function?</u>

- What is the <u>Next State</u> <u>Function?</u>

• Mealy or Moore?

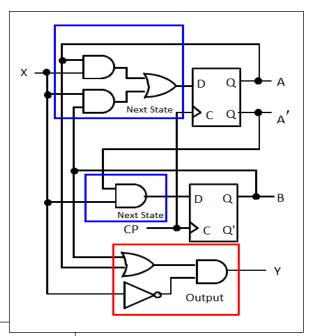

#### Example 1 (continued)

#### Step 1:

• Input flip-flop equations:

$$D_A=Ax+Bx$$

$D_B=A'x$

#### Step 2:

• State equations:

$$A(t+1) = D_A = Ax + Bx$$

$$B(t+1) = D_B = A' x$$

Output equations: y = x' (B + A)

#### Step 3:

• State Table and State Diagram

#### State Table Characteristics

- *State table* a multiple variable table with the following four sections:

- *Present State* the values of the state variables for each allowed state.

- *Input* the input combinations allowed.

- *Next-state* the value of the state at time (t+1) based on the <u>present state</u> and the <u>input</u>.

- *Output* the value of the output as a function of the <u>present state</u> and (sometimes) the <u>input</u>.

- Considered as a truth table:

- the inputs are Input, Present State

- and the outputs are Output, Next State

#### **Example 1: State Table.**

• The state table can be filled in using state equations and

output equations:

$$\begin{split} A(t+1) &= D_A = A(t)x(t) + B(t)x(t) \\ B(t+1) &= D_B = A(t)'x(t) \\ y(t) &= x(t)'(B(t) + A(t)) \end{split}$$

| Present State | Input | Next   | State  | Output |

|---------------|-------|--------|--------|--------|

| A(t) B(t)     | x(t)  | A(t+1) | B(t+1) | y(t)   |

| 0 0           | 0     | 0      | 0      | 0      |

| 0 0           | 1     | 0      | 1      | 0      |

| 0 1           | 0     | 0      | 0      | 1      |

| 0 1           | 1     | 1      | 1      | 0      |

| 1 0           | 0     | 0      | 0      | 1      |

| 1 0           | 1     | 1      | 0      | 0      |

| 1 1           | 0     | 0      | 0      | 1      |

| 1 1           | 1     | 1      | 0      | 0      |

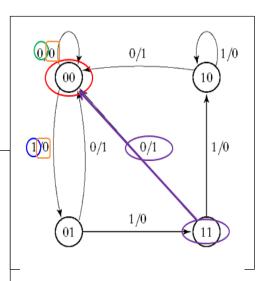

#### **State Diagrams**

- The sequential circuit function can be represented in graphical form as a <u>state diagram</u> with the following components:

- A <u>circle</u> with the state name in it for each state

- A <u>directed arc</u> from the <u>Present State</u> to the <u>Next State</u> for each <u>state transition</u>

- A label on each <u>directed arc</u> with the <u>Input</u> values which causes the <u>state transition</u>, and

- A label:

- On each <u>directed arc</u> with the <u>output</u> value produced (Mealy), or

- On each <u>circle</u> with the <u>output</u> value produced (Moore)

#### **Example 1: State Diagram**

- On <u>directed arc</u> with the <u>output</u> included:

- input/output

- Mealy type output depends on state and input

| Preser         | nt State   | Input | Next             | State            | Output |

|----------------|------------|-------|------------------|------------------|--------|

| A <sub>t</sub> | <u>B</u> ţ | Xţ    | A <sub>t+1</sub> | B <sub>t+1</sub> | Ϋ́t    |

| 0              | 0          | 0     | 0                | 0                | 0      |

| 0              | 0)         | 1     | 0                | 1                | 0      |

| 0              | 1          | 0     | 0                | 0                | 1      |

| 0              | 1          | 1     | 1                | 1                | 0      |

| 1              | 0          | 0     | 0                | 0                | 1      |

| 1              | 0          | 1     | 1                | 0                | 0      |

| 1              | 1          | 0     | 0                | 0                | 1      |

| 1              | 1          | 1     | 1                | 0                | 0      |

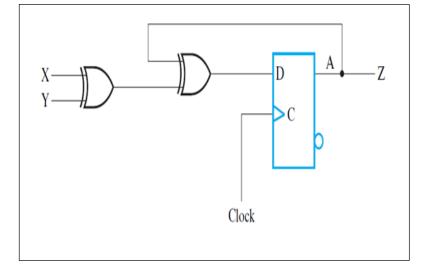

#### Example 2

O Input: x, y

Output: Z

O State: A

• What is the <u>Output</u> <u>Function</u>?

• What is the <u>Next State</u> <u>Function</u>?

• Mealy or Moore?

#### Example 2 (continued)

#### Step 1:

• Input flip-flop equations:  $D_A=x\oplus y\oplus A$

# X D A Z

#### Step 2:

State equations:

A(t+1) =D<sub>A</sub>=x⊕y⊕A

Output equations:

Z(t)=A(t)

#### Step 3:

• State Table and State Diagram

# **Example 2: State Table**

• The state table can be filled in using state equations and output equation:

$$\begin{split} &A(t+1) = &D_A = x(t) \oplus y(t) \oplus A(t) \\ &Z(t) = &A(t) \end{split}$$

| Present<br>state | Inputs |   | Next<br>state | Output |  |

|------------------|--------|---|---------------|--------|--|

| A                | X      | Y | A             | Z      |  |

| 0                | 0      | 0 | 0             | 0      |  |

| 0                | 0      | 1 | 1             | 0      |  |

| 0                | 1      | 0 | 1             | 0      |  |

| 0                | 1      | 1 | 0             | 0      |  |

| 1                | 0      | 0 | 1             | 1      |  |

| 1                | 0      | 1 | 0             | 1      |  |

| 1                | 1      | 0 | 0             | 1      |  |

| 1                | 1      | 1 | 1             | 1      |  |

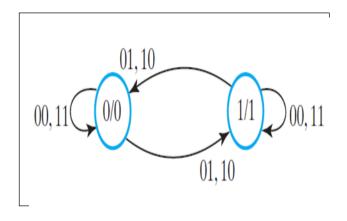

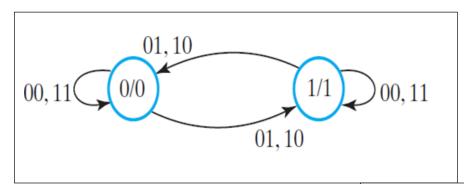

# **Example 2: State Diagram**

- On <u>circle</u> with output included:

- state/output

- Moore type output depends only on state

| Present<br>state | Inp | outs | Next<br>state | Output |

|------------------|-----|------|---------------|--------|

| A                | X   | Y    | A             | Z      |

| 0                | 0   | 0    | 0             | 0      |

| 0                | 0   | 1    | 1             | 0      |

| 0                | 1   | 0    | 1             | 0      |

| 0                | 1   | 1    | 0             | 0      |

| 1                | 0   | 0    | 1             | 1      |

| 1                | 0   | 1    | 0             | 1      |

| 1                | 1   | 0    | 0             | 1      |

| 1                | 1   | 1    | 1             | 1      |